## S1C17 マニュアル 正誤表

| 項目 パッケージ                   |           |                                        |      |  |

|----------------------------|-----------|----------------------------------------|------|--|

| 対象マニュアル                    | 発行 No.    | 項目                                     | ページ  |  |

| S1C17705/703<br>テクニカルマニュアル | 411706502 | 1.1 特長<br>表 1.1.1 特長、出荷形態 1<br>サイズ/ピッチ | 1-2  |  |

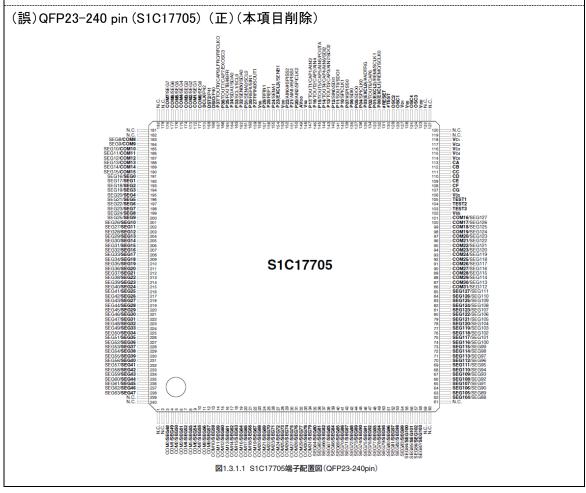

|                            |           | 1.3 端子/パッド<br>1.3.1 S1C17705 端子配置図     | 1-4  |  |

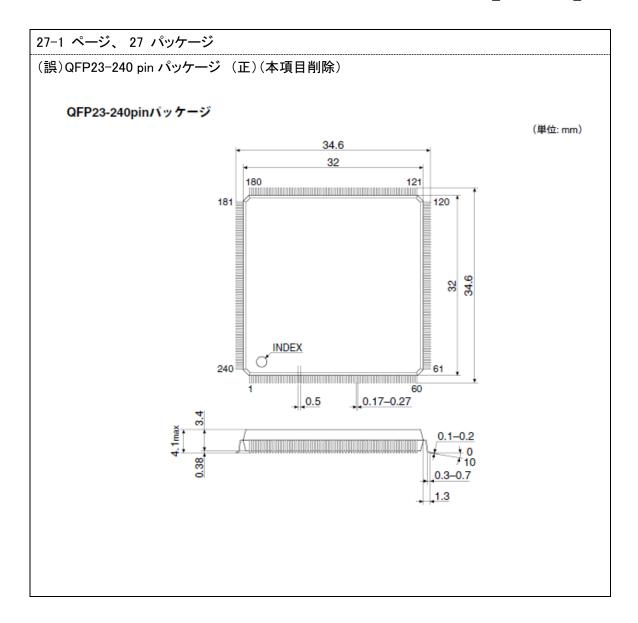

|                            |           | 27 パッケージ                               | 27-1 |  |

1-2 ページ、表 1.1.1 特長、 出荷形態 1

(誤)QFP23-240 pin (正)(本項目削除)

1-2 ページ、表 1.1.1 特長、 サイズ/ピッチ

(誤)QFP23-240 pin (ボディサイズ: 32mm × 32mm, 端子ピッチ: 0.5mm)

(正)(本項目削除)

1-4ページ、1.3.1 S1C17705 端子配置図

# **S1C17** ファミリテクニカルマニュアル正誤表

| 項目 LCD 駆動電圧             |           |                 |       |  |

|-------------------------|-----------|-----------------|-------|--|

| 対象マニュアル                 | 発行 No.    | 項目              | ページ   |  |

| S1C17701 テクニカルマニュアル     | 412445600 | 26.4 アナログ回路特性   | 26-3  |  |

| S1C17702 テクニカルマニュアル     | 411602402 | 27.4 アナログ回路特性   | 27-3  |  |

| S1C17704 テクニカルマニュアル     | 411511804 | 26.4 アナログ回路特性   | 26-3  |  |

| S1C17705/703 テクニカルマニュアル | 411706502 | 25.9 LCD ドライバ特性 | 25-10 |  |

| S1C17706 テクニカルマニュアル     | 412026301 | 27.9 LCD ドライバ特性 | 27-7  |  |

|                         |           |                 |       |  |

## (誤)

特記なき場合: VDD = 1.8~3.6V, Vss = 0V, Ta = 25°C, C1~C11 = 0.1μF, 市松模様出力時, パネル負荷なし

| 1000 0.5 mg. 100 = 110 0.01, 100 = 01, 10 = 20 0, 0.1 0.1 = 0.1 p., 10 mg. 10 mg. |                 |                                   |         |      |         |    |

|-----------------------------------------------------------------------------------|-----------------|-----------------------------------|---------|------|---------|----|

| 項目                                                                                | 記号              | 条件                                | Min.    | Тур. | Max.    | 単位 |

| LCD駆動電圧                                                                           | V <sub>C1</sub> | Vss~Vc <sub>1</sub> 間に1MΩの負荷抵抗を接続 | 0.18Vc5 |      | 0.22Vc5 | V  |

|                                                                                   | Vc2             | Vss~Vc2間に1MΩの負荷抵抗を接続              | 0.39Vc5 |      | 0.43Vc5 | V  |

|                                                                                   | Vcз             | Vss~Vc3間に1MΩの負荷抵抗を接続              | 0.59Vc5 |      | 0.63Vc5 | V  |

|                                                                                   | Vc4             | Vss~Vc4間に1MΩの負荷抵抗を接続              | 0.79Vc5 |      | 0.83Vc5 | V  |

|                                                                                   | Vc5             | Vss~Vcs間に1MΩの負荷 LC[3:0] = 0x0     |         | 4.20 |         | V  |

|                                                                                   |                 | 抵抗を接続 LC[3:0] = 0x1               |         | 4.30 |         | V  |

| I                                                                                 | 1               | 1                                 |         |      |         |    |

### (正)

特記なき場合: VDD = 1.8~3.6V, Vss = 0V, Ta = 25°C, C1~C11 = 0.1μF, 市松模様出力時, パネル負荷なし

| 項目                                | 記号              | 条件                               | Min.    | Тур. | Max.    | 単位 |

|-----------------------------------|-----------------|----------------------------------|---------|------|---------|----|

| LCD駆動電圧                           | V <sub>C1</sub> | <del>Vss-Ver</del> 間に1MΩの負荷抵抗を接続 | 0.18Vcs |      | 0.22Vc5 | ٧  |

| V <sub>2</sub> , V <sub>3</sub> , | V <sub>C2</sub> | Vss~Vc2間に1MΩの負荷抵抗を接続             | 0.39Vc5 |      | 0.43Vc5 | ٧  |

| VC5~VC1                           | Vсз             | Vss~Vc3間に1MΩの負荷抵抗を接続             | 0.59Vc5 |      | 0.63Vc5 | V  |

|                                   | Vc4             | Vss~Vc4間に1MΩの負荷抵抗を接続             | 0.79Vc5 |      | 0.83Vc5 | ٧  |

|                                   | V <sub>C5</sub> | Vss~Vcs間に1MΩの負荷 LC[3:0] = 0x0    |         | 4.20 |         | V  |

|                                   |                 | 抵抗を接続 LC[3:0] = 0x1              |         | 4.30 |         | V  |

| 1                                 | ı               | I                                | 1       |      | 1       |    |

## **S1C17** シリーズテクニカルマニュアル正誤表

| 項目 T16A/T16A2の CBUFEN レジスタについて |           |               |       |  |

|--------------------------------|-----------|---------------|-------|--|

| 対象マニュアル                        | 発行 No.    | 項目            | ページ   |  |

| S1C17624/604/622/602/621 テクニカ  | 411914802 | 13.8 制御レジスタ詳細 | 13-15 |  |

| ルマニュアル                         |           |               |       |  |

| S1C17705/703 テクニカルマニュアル        | 411706502 | 10.8 制御レジスタ詳細 | 10-18 |  |

|                                |           |               |       |  |

| S1C17706 テクニカルマニュアル            | 412026301 | 10.8 制御レジスタ詳細 | 10-17 |  |

|                                |           |               |       |  |

| S1C17711 テクニカルマニュアル            | 411905502 | 10.8 制御レジスタ詳細 | 10-14 |  |

|                                |           |               |       |  |

| S1C17554/564 テクニカルマニュアル        | 411914302 | 11.8 制御レジスタ詳細 | 11-14 |  |

|                                |           |               |       |  |

| S1C17651 テクニカルマニュアル            | 412120500 | 12.8 制御レジスタ詳細 | 12-13 |  |

|                                |           |               |       |  |

13-15 ページ S1C17624/604/622/602/621 テクニカルマニュアル

**10-17 ページ** S1C17706 テクニカルマニュアル

**12-13 ページ** S1C17651 テクニカルマニュアル

(誤)

## D3 CBUFEN: Compare Buffer Enable Bit

コンペアバッファを有効/無効に設定します。

1(R/W): 有効

0(R/W): 無効(デフォルト)

CBUFENを1に設定するとコンペアバッファが有効になり、コンパレータはコンペアA、コンペアBレジスタの代わりにコンペアA、コンペアBバッファとカウンタ値を比較してコンペアA、コンペアB信号を生成します。ソフトウェアでコンペアA、コンペアBレジスタに書き込んだ比較値は、コンペアB信号が発生した時点でコンペアA、コンペアBバッファにロードされます。

CBUFEN を 0 に設定するとコンペアバッファが無効となり、コンパレータはコンペア A、コンペア B レジスタとカウンタ値を比較してコンペア A、コンペア B 信号を生成します。

注: CBUFEN の設定は、カウンタが停止中(PRUN = 0)に行ってください。

(正)

## D3 CBUFEN: Compare Buffer Enable Bit

コンペアバッファを有効/無効に設定します。

1(R/W): 有効

0(R/W): 無効(デフォルト)

CBUFENを1に設定するとコンペアバッファが有効になり、コンパレータはコンペアA、コンペアBレジスタの代わりにコンペアA、コンペアBバッファとカウンタ値を比較してコンペアA、コンペアB信号を生成します。ソフトウェアでコンペアA、コンペアBレジスタに書き込んだ比較値は、コンペアB信号が発生した時点でコンペアA、コンペアBバッファにロードされます。

CBUFEN を 0 に設定するとコンペアバッファが無効となり、コンパレータはコンペア A、コンペア B レジスタとカウンタ値を比較してコンペア A、コンペア B 信号を生成します。

注: CBUFEN の設定は、カウンタが停止中(CLKEN = 0)に行ってください。

**10-18 ページ** S1C17705/703 テクニカルマニュアル

**10-14 ページ** S1C17711 テクニカルマニュアル

11-14 ページ S1C17554/564 テクニカルマニュアル

(誤)

#### D3 CBUFEN: Compare Buffer Enable Bit

コンペアバッファへの書き込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

CBUFENが1に設定されていると、コンペアデータの書き込みがコンペアデータバッファに対して行われます。 バッファの内容は、コンペアB信号が発生した時点でコンペアAおよびコンペアBレジスタにロードされます。 CBUFENが0に設定されている場合は、コンペアデータの書き込みがコンペアAおよびコンペアBレジスタに対して直接行われます。

注: CBUFEN の設定は、カウンタが停止中(PRUN = 0)に行ってください。

(正)

#### D3 CBUFEN: Compare Buffer Enable Bit

コンペアバッファへの書き込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

CBUFENが1に設定されていると、コンペアデータの書き込みがコンペアデータバッファに対して行われます。 バッファの内容は、コンペアB信号が発生した時点でコンペアAおよびコンペアBレジスタにロードされます。 CBUFENが0に設定されている場合は、コンペアデータの書き込みがコンペアAおよびコンペアBレジスタに対して直接行われます。

注: CBUFEN の設定は、カウンタが停止中(CLKEN = 0)に行ってください。

## S1C17 シリーズテクニカルマニュアル正誤表

| 項目 SPI スレーブモード時の送信バッファエンプティ割り込み |           |               |       |  |  |

|---------------------------------|-----------|---------------|-------|--|--|

| 対象マニュアル                         | 発行 No.    | 項目            | ページ   |  |  |

| S1C17003 テクニカルマニュアル             | 411635002 | 19.6 SPI 割り込み | 19-8  |  |  |

|                                 |           | 19.7 制御レジスタ詳細 | 19-13 |  |  |

|                                 |           | 19.8 注意事項     | 19-15 |  |  |

| S1C17705/703 テクニカルマニュアル         | 411706502 | 15.6 SPI 割り込み | 15-5  |  |  |

|                                 |           | 15.7 制御レジスタ詳細 | 15-8  |  |  |

#### **19-8 ページ** S1C17003 テクニカルマニュアル

(誤)

### 送信バッファエンプティ割り込み

この割り込みを使用するには、SPTIE(D4/SPI\_CTLレジスタ)を1に設定します。SPTIEが0(デフォルト)に設定されていると、この要因による割り込み要求はITCに送られません。

\* SPTIE: Transmit Data Buffer Empty Interrupt Enable Bit in the SPI Control (SPI\_CTL) Register (D4/0x4326)

送信データバッファに書き込まれた送信データがシフトレジスタに転送されると、SPIモジュールは SPTBEビット(DO/SPI\_STレジスタ)を1にセットして送信データバッファが空であることを示します。送 信バッファエンプティ割り込みが許可されていれば(SPTIE = 1)、これと同時に割り込み要求がITCに 出力されます。

\* **SPTBE**: Transmit Data Buffer Empty Flag in the SPI Status (SPI\_ST) Register (D0/0x4320) もし、他の割り込み条件が満たされていれば、割り込みが発生します。

SPI 割り込みが送信バッファエンプティによるものかどうかについては、SPI 割り込み処理ルーチンで SPTBE フラグを読み出して確認してください。SPTBE が 1 であれば、割り込み処理ルーチンで次の 送信データを送信データバッファに書き込むことができます。

(正)

## 送信バッファエンプティ割り込み

この割り込みを使用するには、SPTIE(D4/SPI\_CTLレジスタ)を1に設定します。SPTIEが0(デフォルト)に設定されていると、この要因による割り込み要求はITCに送られません。

\* **SPTIE**: Transmit Data Buffer Empty Interrupt Enable Bit in the SPI Control (SPI\_CTL) Register (D4/0x4326)

送信データバッファに書き込まれた送信データがシフトレジスタに転送されると、SPIモジュールは SPTBEビット(DO/SPI\_STレジスタ)を1にセットして送信データバッファが空であることを示します。送 信バッファエンプティ割り込みが許可されていれば(SPTIE = 1)、これと同時に割り込み要求がITCに 出力されます。

\* **SPTBE**: Transmit Data Buffer Empty Flag in the SPI Status (SPI\_ST) Register (D0/0x4320) もし、他の割り込み条件が満たされていれば、割り込みが発生します。

SPI割り込みが送信バッファエンプティによるものかどうかについては、SPI割り込み処理ルーチンで SPTBEフラグを読み出して確認してください。SPTBEが1であれば、割り込み処理ルーチンで次の送信データを送信データバッファに書き込むことができます。

注: 送信バッファエンプティ割り込みは、マスタモード時にのみ使用可能です。

#### **19-13 ページ** S1C17003 テクニカルマニュアル

(誤)

#### D4 SPTIE: Transmit Data Buffer Empty Interrupt Enable Bit

送信データバッファエンプティによるSPI割り込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

SPTIEを1に設定すると、送信データバッファエンプティによるSPI割り込み要求のITCへの出力を許可します。この割り込み要求は、送信データバッファに書き込んだデータがシフトレジスタに転送される(送信を開始する)ことにより発生します。

SPTIEをOに設定すると、送信データバッファエンプティによるSPI割り込みは発生しません。

(正)

#### D4 SPTIE: Transmit Data Buffer Empty Interrupt Enable Bit

送信データバッファエンプティによるSPI割り込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

SPTIEを1に設定すると、送信データバッファエンプティによるSPI割り込み要求のITCへの出力を許可します。この割り込み要求は、送信データバッファに書き込んだデータがシフトレジスタに転送される(送信を開始する)ことにより発生します。

SPTIE を 0 に設定すると、送信データバッファエンプティによる SPI 割り込みは発生しません。 注: 送信バッファエンプティ割り込みは、マスタモード時にのみ使用可能です。

#### **19-15 ページ** S1C17003 テクニカルマニュアル

(誤)

- ・ SPBSYフラグ(D2/SPI\_STレジスタ)が1の間およびSPRBFフラグ(D1/SPI\_STレジスタ)が1の間(データの送受信中)は、SPI CTLレジスタ(0×4326)にアクセスしないでください。

- \* SPBSY: Transfer Busy Flag in the SPI Status (SPI\_ST) Register (D2/0x4320)

- \* SPRBF: Receive Data Buffer Full Flag in the SPI Status (SPI ST) Register (D1/0x4320)

- ・ SPI でデータの送受信を行っている最中に Read レジスタ(SPI\_ST、SPI\_RXD)に、Write アクセスを行わないで下さい。

#### (正)

- ・ SPBSYフラグ(D2/SPI\_STレジスタ)が1の間およびSPRBFフラグ(D1/SPI\_STレジスタ)が1の間(データの送受信中)は、SPI\_CTLレジスタ(0×4326)にアクセスしないでください。

- \* SPBSY: Transfer Busy Flag in the SPI Status (SPI\_ST) Register (D2/0x4320)

- \* SPRBF: Receive Data Buffer Full Flag in the SPI Status (SPI\_ST) Register (D1/0x4320)

- ・ SPI でデータの送受信を行っている最中に Read レジスタ(SPI\_ST、SPI\_RXD)に、Write アクセスを行わないで下さい。

- ・ 送信バッファエンプティ割り込みは、マスタモード時にのみ使用可能です。

**15-5 ページ** S1C17705/703テクニカルマニュアル

(誤)

#### 送信バッファエンプティ割り込み

この割り込みを使用するには、SPTIE/SPI\_CTLxレジスタを1に設定します。SPTIEが0(デフォルト)に 設定されていると、この要因による割り込み要求はITCに送られません。

送信データバッファに書き込まれた送信データがシフトレジスタに転送されると、SPIモジュールは SPTBE/SPI\_STxレジスタ)を1にセットして送信データバッファが空であることを示します。送信バッファエンプティ割り込みが許可されていれば(SPTIE = 1)、これと同時に割り込み要求がITCに出力されます。

もし、他の割り込み条件が満たされていれば、割り込みが発生します。

SPI割り込みが送信バッファエンプティによるものかどうかについては、SPI割り込み処理ルーチンで SPTBEフラグを読み出して確認してください。SPTBEが1であれば、割り込み処理ルーチンで次の送信データを送信データバッファに書き込むことができます。

(正)

#### 送信バッファエンプティ割り込み

この割り込みを使用するには、SPTIE/SPI\_CTLxレジスタを1に設定します。SPTIEが0(デフォルト)に 設定されていると、この要因による割り込み要求はITCに送られません。

送信データバッファに書き込まれた送信データがシフトレジスタに転送されると、SPIモジュールは SPTBE/SPI\_STxレジスタ)を1にセットして送信データバッファが空であることを示します。送信バッファエンプティ割り込みが許可されていれば(SPTIE = 1)、これと同時に割り込み要求がITCに出力されます。

もし、他の割り込み条件が満たされていれば、割り込みが発生します。

SPI割り込みが送信バッファエンプティによるものかどうかについては、SPI割り込み処理ルーチンで SPTBEフラグを読み出して確認してください。SPTBEが1であれば、割り込み処理ルーチンで次の送信データを送信データバッファに書き込むことができます。

注: 送信バッファエンプティ割り込みは、マスタモード時にのみ使用可能です。

**15-8 ページ** S1C17705/703テクニカルマニュアル

#### (誤)

### D4 SPTIE: Transmit Data Buffer Empty Interrupt Enable Bit

送信データバッファエンプティによるSPI割り込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

SPTIEを1に設定すると、送信データバッファエンプティによるSPI割り込み要求のITCへの出力を許可します。この割り込み要求は、送信データバッファに書き込んだデータがシフトレジスタに転送される(送信を開始する)ことにより発生します。

SPTIEをOに設定すると、送信データバッファエンプティによるSPI割り込みは発生しません。

#### (正)

#### D4 SPTIE: Transmit Data Buffer Empty Interrupt Enable Bit

送信データバッファエンプティによるSPI割り込みを許可/禁止します。

1(R/W): 許可

0(R/W): 禁止(デフォルト)

SPTIEを1に設定すると、送信データバッファエンプティによるSPI割り込み要求のITCへの出力を許可します。この割り込み要求は、送信データバッファに書き込んだデータがシフトレジスタに転送される(送信を開始する)ことにより発生します。

SPTIEをOに設定すると、送信データバッファエンプティによるSPI割り込みは発生しません。

注: 送信バッファエンプティ割り込みは、マスタモード時にのみ使用可能です。